AVR Flash Memory Notes Part One Exploring the Atmega328P pete@soper.us February 12, 2018

#### Outline

- Touch on flash operation

- Flash characteristics

- Addressing and access

- Fuses and other special locations

- Unless otherwise noted all specifics are to do with the (Atmel cum Microchip) AVR Atmega328 MPU

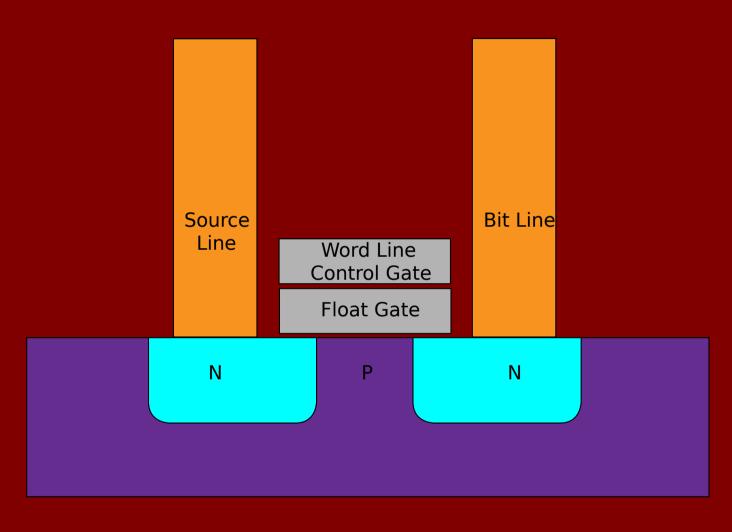

# Flash Memory Cell (Wikipedia)

## **Memory Operation**

- FET transistor with two gates:

- Isolated gate that holds a charge

- Control gate used for access

- Counterintuitive storage:

- Erased cell without charge is HIGH

- Cell with charge is LOW

- So HIGH "bit" is simply "written with nothing" to preserve logic state

## Characteristic: Speed

- Read speed of flash inside Atmega328 is "adequate"

- Supports 50ns read access to avoid "wait states"

- Write speed is slower

- Erase speed is also much slower

- These characteristics hold for other examples of flash and different types, but some varieties have fast write as well as fast read performance

- I'm too lazy to time writes/erases, but maybe for a "part 2" talk

#### Characteristic: Endurance

- Read endurance until transistor charge is lost. For Atmega328:

- 1 PPM error over 20 years @ 85C,

100 years at 25C

- Limited erase/write cycles before cells "wear out"

- "At least 10,000 cycles" for Atmega328 (probably for all AVR family members, but not sure)

- I don't know about you folks, but I'd CRC-check my flash during POST for a critical app with a long lifespan

## Addressing

- Atmega328 flash is composed of 16 bit words

- Intended application is fetching instructions and AVR instructions are one or more 16 bit words

- Granularity of read and write access

- Words arranged into 64 word (128 byte) pages

- This is the erase granularity

- Pages are arranged into two sections: "application" and "bootloader"

- Size options for bootloader section

## More Addressing

- Because read/write access granularity is a 16 bit word, there is no need for byte addresses

- All flash-related addresses with in 328 instructions are WORD ADDRESSES

- Expressed as byte addresses frequenty to keep us sane

- But encoded addresses are word addresses

- Nice side effect is that Atmega328 first cousins (e.g. 1284) can access 128KB of flash without muss or fuss

#### Sections

- Application section is designed to hold you know what

- Bootloader section is designed to hold:

- Bootloaders (duh)

- ANY CODE TO WRITE TO FLASH

- This means a vanilla application cannot change its own flash memory

- Common bootloaders do not provide flash write routines usable by application code

## Special Regions

- A few special flash memory regions

- ID signature (MCU type & package)

- Fuses to set major chip parameters

- Fuses to control access ("locks")

- KEY POINT: Some fuses disable access

- So wrong setting hoses you and forces special "high voltage erase" to recover

- KEY POINT (for me): Default settings frequently preclude application code modifying flash

## Brief Outline of Write Operations

- SPM instruction stores words into flash

- AVR has a Harvard architecture: program and data are in separate address spaces, so regular store won't work anyway

- Pages can be written a special way:

- Put data to be written into a special, page-size "temporary buffer" inside the chip (static RAM not ordinarily accessible)

- Use special form of SPM to copy temp buffer into flash

#### References

- Wikipedia "flash memory" page: https://en.wikipedia.org/wiki/Flash\_m emory

- AVR Instruction set:

https://en.wikipedia.org/wiki/Atmel\_A

VR\_instruction\_set

- Atmega328P datasheet: http://ww1.microchip.com/downloads/ en/DeviceDoc/Atmel-42735-8-bit-AVR-Microcontroller-ATmega328-328P Datasheet.pdf

### Additional Details

Following slides not part of planned presentation but provide a bit more detail

# Regular Feature Fuses

| AVR part name: ATmega328P ▼ Select (141 parts currently listed) |                                                                                       |                                                                                     |                                                             |               |                   |  |  |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------|-------------------|--|--|

| Fea                                                             | ture configuratio                                                                     | n                                                                                   |                                                             |               |                   |  |  |

| This allo                                                       | ws easy configuration of you                                                          | ur AVR device. All chan                                                             | ges will be applied instantly.                              |               |                   |  |  |

| Featu                                                           | ıres                                                                                  |                                                                                     |                                                             |               |                   |  |  |

| Int. F                                                          | RC Osc. 8 MHz; Start-u                                                                | p time PWRDWN/i                                                                     | RESET: 6 CK/14 CK + 65 ms; [CKSEL=00                        | 10 SUT=10]; d | efault value      |  |  |

|                                                                 | Clock output on PORTB0; [CKOUT=0]                                                     |                                                                                     |                                                             |               |                   |  |  |

| <b>₽</b> [                                                      |                                                                                       |                                                                                     |                                                             |               |                   |  |  |

| □ E                                                             | Boot Reset vector Enab                                                                | led (default addre                                                                  | ss=\$0000); [BOOTRST=0]                                     |               |                   |  |  |

| Boot                                                            | Flash section size=204                                                                | 48 words Boot star                                                                  | t address=\$3800; [BOOTSZ=00] ; default                     | value ▼       |                   |  |  |

| □ F                                                             | Preserve EEPROM mem                                                                   | ory through the Cl                                                                  | hip Erase cycle; [EESAVE=0]                                 |               |                   |  |  |

| □ \                                                             | Natch-dog Timer alway                                                                 | s on; [WDTON=0]                                                                     |                                                             |               |                   |  |  |

| <b>₹</b>                                                        | Serial program downloa                                                                | ading (SPI) enabled                                                                 | d; [SPIEN=0]                                                |               |                   |  |  |

|                                                                 | Debug Wire enable; [D\                                                                | WEN=0]                                                                              |                                                             |               |                   |  |  |

| □ F                                                             | Reset Disabled (Enable                                                                | PC6 as i/o pin); [R                                                                 | STDISBL=0]                                                  |               |                   |  |  |

| Brov                                                            | vn-out detection disable                                                              | ed; [BODLEVEL=11                                                                    | <b>11</b> ] ▼                                               |               |                   |  |  |

|                                                                 | means unprogrammed (1                                                                 |                                                                                     | se bits. All changes will be applied instantly.<br>med (0). | Extended      |                   |  |  |

| 7                                                               | ✓ CKDIV8                                                                              | RSTDISBL                                                                            |                                                             | Exteriocu     |                   |  |  |

|                                                                 | Divide clock by 8                                                                     | External reset disab                                                                | le                                                          |               |                   |  |  |

| 6                                                               | CKOUT Clock output                                                                    | □ DWEN                                                                              |                                                             |               |                   |  |  |

| 5                                                               |                                                                                       | debugWIRE Enable                                                                    |                                                             |               |                   |  |  |

|                                                                 | SuT1 Select start-up time                                                             | <b>SPIEN</b>                                                                        | mming and Data Downloading                                  |               |                   |  |  |

| 4                                                               | SUT1                                                                                  | <b>SPIEN</b>                                                                        |                                                             |               |                   |  |  |

| 4                                                               | SUT1 Select start-up time SUT0                                                        | SPIEN Enable Serial progra WDTON Watchdog Timer Alw                                 |                                                             |               |                   |  |  |

|                                                                 | SUT1 Select start-up time  SUT0 Select start-up time  CKSEL3                          | SPIEN Enable Serial progra WDTON Watchdog Timer Alw                                 | rays On                                                     | BODLEVE       |                   |  |  |

| 3                                                               | SUT1 Select start-up time SUT0 Select start-up time CKSEL3 Select Clock Source CKSEL2 | SPIEN Enable Serial progra WDTON Watchdog Timer Alw EESAVE EEPROM memory is BOOTSZ1 | rays On                                                     |               | tor trigger level |  |  |

## Special Feature Fuses

#### **Program And Data Memory Lock Bits**

The ATmega 48A/48PA provides two Lock bits and the ATmega88A/88PA/168A/168PA/328/328Pprovides six Lock bits. These can be left unprogrammed ("1") or can be programmed ("0") to obtain the additional features listed in Table 28-2. The Lock bits can only be erased to "1" with the Chip Erase command.

The ATmega 48A/48PA has no separate Boot Loader section, and the SPM instruction is enabled for the whole Flash if the SELFPRGEN fuse is programmed ("0"). Otherwise the SPM instruction is disabled.

Lock Bit Byte(1) Table 28-1.

| Lock Bit Byte        | Bit No | Description   | Default Value    |

|----------------------|--------|---------------|------------------|

|                      | 7      | -             | 1 (unprogrammed) |

|                      | 6      | -             | 1 (unprogrammed) |

| BLB12 <sup>(2)</sup> | 5      | Boot Lock bit | 1 (unprogrammed) |

| BLB11 <sup>(2)</sup> | 4      | Boot Lock bit | 1 (unprogrammed) |

| BLB02 <sup>(2)</sup> | 3      | Boot Lock bit | 1 (unprogrammed) |

| BLB01 <sup>(2)</sup> | 2      | Boot Lock bit | 1 (unprogrammed) |

| LB2                  | 1      | Lock bit      | 1 (unprogrammed) |

| LB1                  | 0      | Lock bit      | 1 (unprogrammed) |

"1" means unprogrammed, "0" means programmed.

Only on ATmega88A/88PA/168A/168PA/328/328P.

Lock Bit Protection Modes(1)(2) Table 28-2.

| Memory Lock Bits |     |     | Protection Type                                                                                                                                                                                                            |

|------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LB Mode          | LB2 | LB1 |                                                                                                                                                                                                                            |

| 1                | 1   | 1   | No memory lock features enabled.                                                                                                                                                                                           |

| 2                | 1   | 0   | Further programming of the Flash and EEPROM is disabled in Parallel and Serial Programming mode. The Fuse bits are locked in both Serial and Parallel Programming mode. (1)                                                |

| 3                | 0   | 0   | Further programming and verification of the Flash and EEPROM is disabled in Parallel and Serial Programming mode. The Boot Lock bits and Fuse bits are locked in both Serial and Parallel Programming mode. <sup>(1)</sup> |

- Program the Fuse bits and Boot Lock bits before programming the LB1 and LB2.

- 2. "1" means unprogrammed, "0" means programmed

# How To Mess Up Your Chip

| AVR part name: ATmega328P ▼ Select (141 parts currently listed) |                                                                                                             |                                                          |                                  |  |  |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------|--|--|--|

| Feature configuration                                           |                                                                                                             |                                                          |                                  |  |  |  |

| This all                                                        | ows easy configuration of you                                                                               | r AVR device. All changes will be applied instantly.     |                                  |  |  |  |

| Feat                                                            | ıres                                                                                                        |                                                          |                                  |  |  |  |

| Int. I                                                          | RC Osc. 8 MHz; Start-up                                                                                     | time PWRDWN/RESET: 6 CK/14 CK + 65 ms; [CKSEL=0          | 010 SUT=10]; default value ▼     |  |  |  |

|                                                                 |                                                                                                             |                                                          |                                  |  |  |  |

| •                                                               | Divide clock by 8 interna                                                                                   | ally; [CKDIV8=0]                                         |                                  |  |  |  |

|                                                                 | Boot Reset vector Enabl                                                                                     | ed (default address=\$0000); [BOOTRST=0]                 |                                  |  |  |  |

| Boo                                                             | t Flash section size=204                                                                                    | 8 words Boot start address=\$3800; [BOOTSZ=00] ; default | t value ▼                        |  |  |  |

|                                                                 | Preserve EEPROM memo                                                                                        | ory through the Chip Erase cycle; [EESAVE=0]             |                                  |  |  |  |

|                                                                 | Watch-dog Timer always                                                                                      | s on; [WDTON=0]                                          |                                  |  |  |  |

| •                                                               | Serial program downloa                                                                                      | ding (SPI) enabled; [SPIEN=0]                            |                                  |  |  |  |

|                                                                 | Debug Wire enable; [DV                                                                                      | /EN=0]                                                   |                                  |  |  |  |

|                                                                 | Reset Disabled (Enable                                                                                      | PC6 as i/o pin); [RSTDISBL=0]                            |                                  |  |  |  |

| Brov                                                            | vn-out detection disable                                                                                    | d; [BODLEVEL=111] ▼                                      |                                  |  |  |  |

|                                                                 |                                                                                                             |                                                          | Apply feature settings           |  |  |  |

| Ma                                                              | Manual fuse bits configuration                                                                              |                                                          |                                  |  |  |  |

|                                                                 | This table allows reviewing and direct editing of the AVR fuse bits. All changes will be applied instantly. |                                                          |                                  |  |  |  |

|                                                                 | means unprogrammed (1)                                                                                      | ; Means processmed (0).                                  |                                  |  |  |  |

| Bit                                                             | Low                                                                                                         | nign                                                     | Extended                         |  |  |  |

| 7                                                               | CKDIV8 Divide clock by 8                                                                                    | RSTDISBL                                                 |                                  |  |  |  |

| 6                                                               | CKOUT                                                                                                       | DWEN                                                     |                                  |  |  |  |

|                                                                 | Clock output                                                                                                | debugWIRE Enable                                         |                                  |  |  |  |

| 5                                                               | SUT1 Select start-up ime                                                                                    | SPIEN  Enable F                                          |                                  |  |  |  |

| 4                                                               | <b>愛</b> SUTO                                                                                               | WDTON                                                    |                                  |  |  |  |

|                                                                 | elect start-up me                                                                                           | Watchdog Timeways On                                     |                                  |  |  |  |

| 3                                                               | <b>✓</b> CKSEL3                                                                                             | JAVE                                                     |                                  |  |  |  |

| 2                                                               | Select Clock Source                                                                                         | EEPROM memory is preserved through chip erase            | 0                                |  |  |  |

| _                                                               | ✓ CKSEL2 Select Clock Source                                                                                | <b>☑ BOOTSZ1</b> Select boot size                        | Brown-out Detector trigger level |  |  |  |

| 1                                                               | CKSEL1                                                                                                      | <b>愛</b> BOOTSZ0                                         | BODLEVEL1                        |  |  |  |

|                                                                 | Select Clock Source                                                                                         | Select boot size                                         | Brown-out Detector trigger level |  |  |  |

| 0                                                               | CKSEL0                                                                                                      | BOOTRST                                                  | BODLEVELO                        |  |  |  |

|                                                                 | Select Clock Source                                                                                         | Select reset vector                                      | Brown-out Detector trigger level |  |  |  |

#### Nails In The Coffin

#### 28.1 Program And Data Memory Lock Bits

The ATmega 48A/48PA provides two Lock bits and the ATmega88A/88PA/168A/168PA/328/328Pprovides six Lock bits. These can be left unprogrammed ("1") or can be programmed ("0") to obtain the additional features listed in Table 28-2. The Lock bits can only be erased to "1" with the Chip Erase command.

The ATmega 48A/48PA has no separate Boot Loader section, and the SPM instruction is enabled for the whole Flash if the SELFPRGEN fuse is programmed ("0"). Otherwise the SPM instruction is disabled.

Table 28-1. Lock Bit Byte<sup>(1)</sup>

| Lock Bit Byte        | Bit No | Description   | Default Value    |

|----------------------|--------|---------------|------------------|

|                      | 7      | -             | 1 (unprogrammed) |

|                      | 6      | -             | 1 (unprogrammed) |

| BLB12 <sup>(2)</sup> | 5      | Boot Lock bit | 1 (unprogrammed) |

| BLB11 <sup>(2)</sup> | 4      | Boot Lock bit | 1 (unprogrammed) |

| BLB02 <sup>(2)</sup> | 3      | Boot Lock bit | 1 (unprogrammed) |

| BLB01 <sup>(2)</sup> | 2      | Boot Lock bit | 1 (unprogrammed) |

| LB2                  | 1      | Lock bit      | 1 (unprogrammed) |

| LB1                  | 0      | Lock bit      | 1 (unprogrammed) |

otes: 1. "1" means unprogrammed, "0" means programmed.

Only on ATmega88A/88PA/168A/168PA/328/328P.

Table 28-2. Lock Bit Protection Modes<sup>(1)(2)</sup>

|         | Name and Street Brown Street |     |                                                                                                                                                                                                                            |  |  |

|---------|------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Memo    | ry Lock Bit                  | S   | Protection Type                                                                                                                                                                                                            |  |  |

| LB Mode | LB2                          | LB1 |                                                                                                                                                                                                                            |  |  |

| 1       | 1                            | 1   | No memory lock features enabled.                                                                                                                                                                                           |  |  |

| 2       | 1                            | 0   | Further programming of the Flash and EEPROM is disabled in<br>Parallel and Serial Programming mode. The Fuse bits are<br>locked in both Serial and Parallel Programming mode. (1)                                          |  |  |

| 3       | 0                            | 0   | Further programming and verification of the Flash and EEPROM is disabled in Parallel and Serial Programming mode. The Boot Lock bits and Fuse bits are locked in both Serial and Parallel Programming mode. <sup>(1)</sup> |  |  |

Notes: 1. Program the Fuse bits and Boot Lock bits before programming the LB1 and LB2.

2. "1" means unprogrammed, "0" means programmed